編碼器通信新篇章:BiSS總線技術(shù)深度解析

BiSS通信協(xié)議是一種專為實(shí)時、雙向、高速編碼器通信設(shè)計的全雙工同步串行總線通信協(xié)議。它在硬件層面與工業(yè)標(biāo)準(zhǔn)的SSI(同步串行接口協(xié)議)總線協(xié)議保持兼容,因此特別適用于運(yùn)動控制領(lǐng)域,特別是伺服驅(qū)動器與編碼器之間的通信。

編碼器總線的發(fā)展態(tài)勢與現(xiàn)狀

隨著現(xiàn)場總線技術(shù)的日益成熟和SOC片上系統(tǒng)的廣泛應(yīng)用,控制系統(tǒng)正朝著全數(shù)字化的方向邁進(jìn),這已成為該領(lǐng)域的發(fā)展重點(diǎn)和研究焦點(diǎn)。編碼器作為這一變革中的關(guān)鍵部分,其數(shù)字化發(fā)展帶動了絕對式編碼器和相關(guān)通信總線的技術(shù)革新。鑒于編碼器在運(yùn)動控制中的廣泛應(yīng)用,編碼器總線必須滿足運(yùn)動控制器對精度、分辨率和響應(yīng)速度的高標(biāo)準(zhǔn)需求。具體而言,這些需求可歸結(jié)為以下五大特性:

高速通信:確保更快的響應(yīng)速度。

時延固定:保證編碼值的物理意義準(zhǔn)確性,便于伺服控制器的算法調(diào)整。

數(shù)據(jù)診斷:提高系統(tǒng)的穩(wěn)定性和可靠性。

雙向通信:實(shí)現(xiàn)信息的實(shí)時交互。

低成本:滿足廣泛的市場應(yīng)用需求。

若考慮使用CAN總線進(jìn)行編碼器通信,我們會發(fā)現(xiàn)其通信過程中存在采樣滯后的問題,且這個滯后時間并非固定。相較之下,BiSS在MA(主機(jī)發(fā)出的時鐘)的第一個上升沿即進(jìn)行數(shù)據(jù)采樣,理論上實(shí)現(xiàn)了無延遲的通信。

目前,通用現(xiàn)場總線在高速編碼器通信方面的應(yīng)用仍顯不足。市場上多數(shù)專門用于高速數(shù)據(jù)通信的傳感器總線是由編碼器廠商自行開發(fā)的,因此具有較強(qiáng)的封閉性。盡管如此,也有一些開放且通用的協(xié)議嶄露頭角,如BiSS。BiSS不僅是一個國際通用的協(xié)議,而且其協(xié)議本身是開放的。目前,BiSS通信協(xié)議已發(fā)展至BISS-C版本,其使用無需支付任何許可費(fèi)用。此外,BiSS協(xié)會的會員還能享受免費(fèi)的IP核源代碼和技術(shù)支持,而且會員資格和入會申請均無需繳納費(fèi)用。

BiSS通信協(xié)議的核心技術(shù)特點(diǎn)

二線串行同步數(shù)據(jù)總線設(shè)計,無論是采用RS422接口實(shí)現(xiàn)高達(dá)10Mbit/s的波特率,還是使用LVDS接口實(shí)現(xiàn)超過10Mbit/s的傳輸速率,都充分展現(xiàn)了BiSS出色的響應(yīng)速度。

通信效率極高,每10微秒即可傳輸超過64個比特,有效負(fù)載率高達(dá)80%以上。這充分說明了BiSS能夠輕松承載高分辨率編碼器數(shù)據(jù),滿足高精度控制需求。

線路時分復(fù)用技術(shù)的運(yùn)用,使得數(shù)據(jù)通信信道和寄存器通信信道在每個通信周期內(nèi)得以高效傳輸。兩者完全獨(dú)立,互不干擾。針對無需寄存器通信的應(yīng)用場景,BiSS提供了CUnidirectional版本,進(jìn)一步簡化了通信過程。這一特性提升了控制系統(tǒng)的穩(wěn)定性和操作便利性。

BiSS采用了多種安全機(jī)制,確保數(shù)據(jù)傳輸?shù)目煽啃浴F渲校舆t補(bǔ)償技術(shù)有效彌補(bǔ)了傳輸線帶來的信號延遲問題。同時,兩組CRC生成多項(xiàng)式分別對傳感器數(shù)據(jù)與寄存器數(shù)據(jù)進(jìn)行校驗(yàn),增強(qiáng)了數(shù)據(jù)的完整性。此外,協(xié)議幀中的報警位和錯誤位,以及可自定義的CRC生成多項(xiàng)式,都為數(shù)據(jù)傳輸提供了強(qiáng)大的安全保障。特別是在高安全要求的場合,BiSS還支持使用16位CRC,進(jìn)一步提升數(shù)據(jù)傳輸?shù)目煽啃浴?br />

數(shù)據(jù)同步是BiSS協(xié)議的另一大特點(diǎn)。利用時鐘信號同步傳感器數(shù)據(jù),確保每個傳感器在接收到第一個時鐘脈沖時進(jìn)行數(shù)據(jù)更新。這種設(shè)計使得每一幀數(shù)據(jù)到達(dá)后續(xù)電子設(shè)備的傳輸延遲保持一致,方便進(jìn)行時延補(bǔ)償。因此,BiSS特別適用于對時間位置關(guān)系要求苛刻的應(yīng)用場景,如電機(jī)控制等。

BiSS還具備強(qiáng)大的組網(wǎng)能力。通過構(gòu)建單總線傳感器環(huán)網(wǎng),可以在一個通信周期內(nèi)同步采集所有傳感數(shù)據(jù)。這種設(shè)計不僅提高了數(shù)據(jù)采集的效率,還展現(xiàn)了BiSS的擴(kuò)展性和前瞻性。

最后,BiSS協(xié)議支持即插即用功能。通過從寄存器讀出編碼器參數(shù)來配置數(shù)據(jù)通信,使得支持BiSS標(biāo)準(zhǔn)EDS和Profile的編碼器和控制系統(tǒng)能夠直接通信,無需修改任何程序。這一特性體現(xiàn)了BiSS的高度開放性和兼容性,為用戶提供了極大的便利。

BiSS通信協(xié)議的基本內(nèi)容詳解

一、組網(wǎng)方式概覽

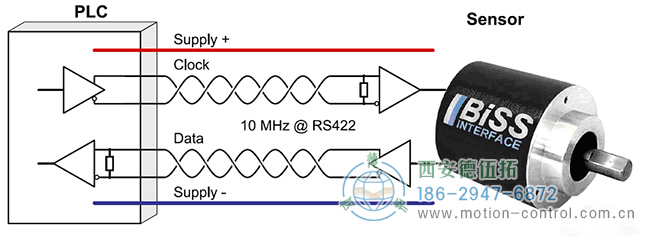

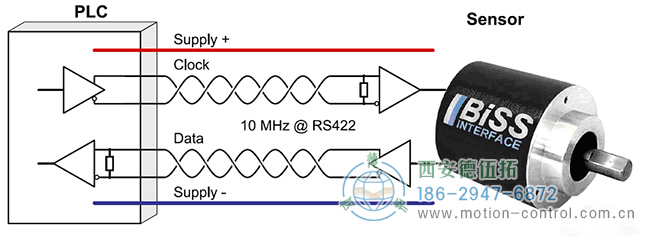

BiSS通信協(xié)議提供了靈活多樣的組網(wǎng)方式,以滿足不同應(yīng)用場景的需求。其中,point-to-point方式是最基本的組網(wǎng)形式,它實(shí)現(xiàn)了單個后續(xù)電子設(shè)備(如PLC)與傳感器之間的點(diǎn)對點(diǎn)通信。在這種方式下,后續(xù)電子設(shè)備作為Master,通過差分信號向作為Slave的傳感器提供時鐘,傳感器則同步地通過差分信號向Master發(fā)送傳感數(shù)據(jù)。這種點(diǎn)對點(diǎn)通信模式不僅支持?jǐn)?shù)據(jù)接收,還實(shí)現(xiàn)了雙向數(shù)據(jù)通信。

圖1point-to-point組網(wǎng)

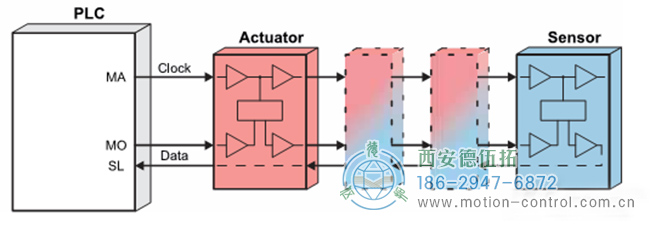

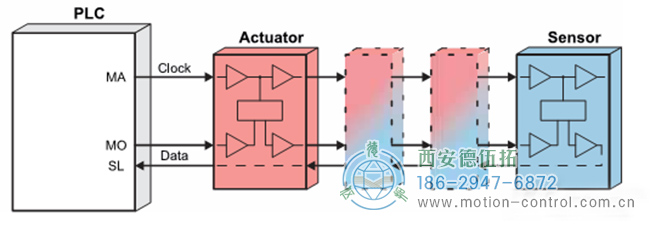

除了point-to-point方式外,BiSS還支持Multi-slaveNetworking多從機(jī)組網(wǎng)方式。在這種模式下,Master可以在一個周期內(nèi)完成與多個Slave之間的通信。所有設(shè)備按照菊花鏈?zhǔn)孜策B接,每個Slave具備兩個端口,分別用于接收前端信號和向后端發(fā)送信號。這種類似流水線的工作方式確保了每個Slave能夠接收上一個Slave的數(shù)據(jù)并將其放入自己的發(fā)送隊列隊尾,同時優(yōu)先發(fā)送自身的數(shù)據(jù)。整個通信過程由Master發(fā)出的時鐘信號進(jìn)行同步,確保數(shù)據(jù)傳輸?shù)臏?zhǔn)確性和可靠性。

圖2Multi-slaveNetworking組網(wǎng)

二、BiSS幀結(jié)構(gòu)與數(shù)據(jù)通信細(xì)節(jié)

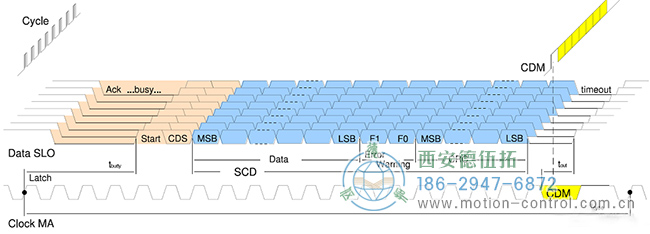

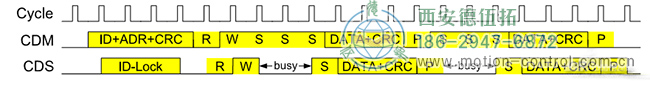

在point-to-point組網(wǎng)方式下,BiSS通信幀的結(jié)構(gòu)如圖3所示。MA信號由Master發(fā)出,用于驅(qū)動通信過程;而SL信號則是Slave發(fā)出的數(shù)據(jù)信號。完成一個BiSS通信幀意味著Master已經(jīng)成功接收到一幀數(shù)據(jù)。

圖3point-to-point組網(wǎng)的BiSS幀結(jié)構(gòu)

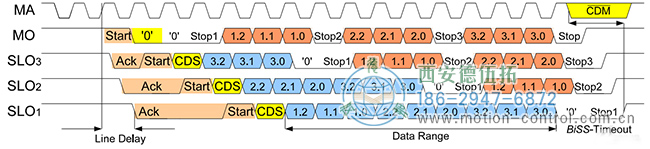

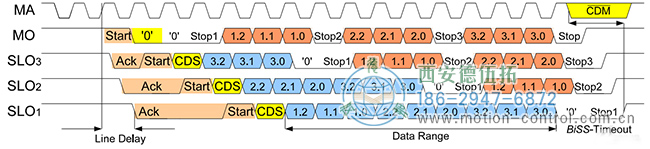

對于Multi-slaveNetworking組網(wǎng)方式,每個Slave不僅需要發(fā)送自己的數(shù)據(jù),還需要接收并轉(zhuǎn)發(fā)前一個Slave發(fā)送過來的數(shù)據(jù)。這種通信模式如圖4所示,展示了在多從機(jī)組網(wǎng)下BiSS通信幀的結(jié)構(gòu)特點(diǎn)。

圖4Multi-slaveNetworking組網(wǎng)的BiSS幀結(jié)構(gòu)

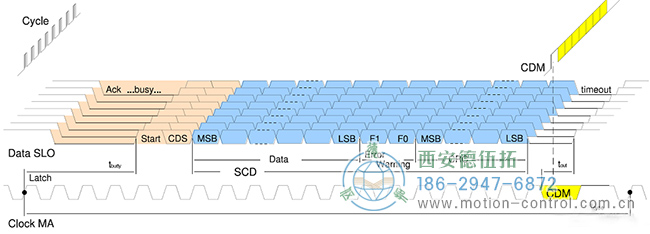

BiSS通信過程涉及多個狀態(tài)的切換,包括IDLE(空閑)、StartFrame(幀開始)、Tranmission(發(fā)送)和Timeout(超時)。在IDLE狀態(tài)下,BiSS通信處于空閑狀態(tài),MA和SL信號均保持高電平。當(dāng)進(jìn)入StartFrame狀態(tài)時,Master通過MA發(fā)送時鐘信號,Slave在MA的第一個上升沿鎖存?zhèn)鞲衅鳡顟B(tài),并在第二個上升沿通過拉低SL信號來應(yīng)答Master的通信請求。

理想情況下,SL拉低與MA第二上升沿之間的時延應(yīng)非常小。然而,在實(shí)際系統(tǒng)中,由于長線延遲、信號整形、濾波以及信號傳遞通過多級門電路等因素的綜合作用,SL信號相對于MA信號會存在一定的相移,導(dǎo)致SL拉低滯后于MA第二上升沿一段時間。這個時延被稱為line-delay線路延遲。為了確保通信的可靠性,BiSS規(guī)定在每個通信幀發(fā)起時都要檢測并修正line-delay,從而確保BiSS通信的波特率可以達(dá)到10Mbit/s。

在Tranmission狀態(tài)下,SL信號從高電平拉低并保持一段時間,這段時間被稱為ACK,表示Slave已經(jīng)響應(yīng)了MA信號并正在進(jìn)行數(shù)據(jù)準(zhǔn)備。ACK期間的長度與Slave數(shù)據(jù)是否準(zhǔn)備就緒有關(guān),對于特定的Slave,其ACK的長度基本上是固定的。在ACK期間,MA持續(xù)輸出脈沖。隨后,SL發(fā)送一個BIT的START位(通常為‘1’),表示Slave數(shù)據(jù)已經(jīng)準(zhǔn)備就緒,并開始發(fā)送數(shù)據(jù)。

在數(shù)據(jù)發(fā)送過程中,SL會依次發(fā)送一個BIT的CDS信號和一個單周期字段(SCD)。BiSS規(guī)定單周期字段的長度應(yīng)大于4個BIT且小于64個BIT。對于特定應(yīng)用,字段長度由Slave廠商規(guī)定。在數(shù)據(jù)發(fā)送期間,MA持續(xù)輸出脈沖。

最后,當(dāng)SCD發(fā)送完成后,SL會維持一段時間的低電平,這個時間段被稱為Timeout。對于特定的應(yīng)用,Timeout的長度由Slave廠商規(guī)定。在Timeout期間,MA發(fā)送CDM信號,該信號一直維持到SL被拉高。當(dāng)SL被拉高后,本次通信完全結(jié)束。

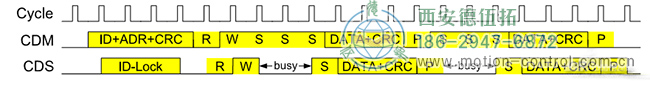

BiSS的寄存器通信機(jī)制

在BiSS通信協(xié)議中,CDM和CDS信號扮演著關(guān)鍵角色,它們是實(shí)現(xiàn)Master與Slave之間寄存器通信的重要信號。當(dāng)Master與Slave進(jìn)行多個周期的數(shù)據(jù)交換后,Slave接收到的Master發(fā)送的CDM序列與Master接收到的Slave發(fā)送的CDS序列共同構(gòu)成了BiSS寄存器通信幀,這一結(jié)構(gòu)如圖5所示。

圖5多個BiSS幀構(gòu)成的寄存器通信序列

通過圖6和圖7的時序描述,我們可以清晰地看到BiSS如何與編碼器進(jìn)行雙向的數(shù)據(jù)交換。BiSS的寄存器通信機(jī)制中,不僅包含CRC校驗(yàn)確保數(shù)據(jù)傳輸?shù)耐暾裕€具備讀回校驗(yàn)功能,特別是在寫時序中,這一機(jī)制進(jìn)一步提升了通信的可靠性。

圖6BiSS寄存器通信寫時序

圖6BiSS寄存器通信寫時序

值得一提的是,BiSS的寄存器通信在帶寬占用方面表現(xiàn)出色,相較于EnData2.2和NRZ等其他通信協(xié)議,它有著顯著的優(yōu)勢。這主要得益于其巧妙的通信策略:在伺服控制器初始化時,編碼器參數(shù)的讀取操作較多;而在正常工作狀態(tài)下,用戶通常更關(guān)注錯誤報警信息。因此,BiSS將錯誤報警信息納入實(shí)時性較高的數(shù)據(jù)通信中,而將耗時的寄存器通信通過CDS和CDM信號實(shí)現(xiàn)。這種根據(jù)數(shù)據(jù)實(shí)時性設(shè)計不同通信速率的方法,不僅大幅節(jié)約了通信帶寬,還有效降低了通信時延。因此,使用BiSS編碼器能顯著提升控制系統(tǒng)的性能和響應(yīng)速度。

圖6展示了BiSS寄存器通信的寫時序,而圖7則呈現(xiàn)了讀時序,通過這些圖示,我們可以更加直觀地理解BiSS寄存器通信的工作原理和時序安排。

BiSS通信協(xié)議的實(shí)現(xiàn)方法

一、硬件解碼方法

對于選擇硬件解碼途徑的用戶,可以根據(jù)實(shí)際應(yīng)用需求選擇IC-HAUS提供的解碼芯片,或利用其提供的IP軟核進(jìn)行解碼操作。同時,市場上也有帶有IP硬核的MCU可供選擇。若用戶希望利用IC-HAUS的IP軟核實(shí)現(xiàn)數(shù)據(jù)通信與寄存器兩種功能,建議采用FPGA解碼方式。但需注意,F(xiàn)PGA的資源數(shù)應(yīng)滿足一定要求,如在將BiSS與MCU接口設(shè)置為SPI時,資源數(shù)需大于1300個LE。若僅關(guān)注數(shù)據(jù)通信功能,CPLD解碼則是一個更為經(jīng)濟(jì)的選擇,但同樣要確保其資源數(shù)滿足最低要求。自行設(shè)計解碼方案時,需特別注意線延遲的處理,特別是在外引線較長或存在變化的應(yīng)用中,需進(jìn)行周期性的線延遲補(bǔ)償。

二、軟件解碼方法

盡管用戶可以選擇通過IO模擬BiSS時序來實(shí)現(xiàn)解碼,但這種方法在實(shí)際應(yīng)用中并不推薦。相比之下,采用MCU的硬件外設(shè)進(jìn)行解碼是更為高效和可靠的選擇。通過利用MCU的硬件外設(shè),用戶可以將BiSS通信速度設(shè)定在較高水平,同時顯著減少外部邏輯電路的成本。對于許多應(yīng)用來說,這種成本節(jié)約是相當(dāng)可觀的,并且有助于產(chǎn)品的系列化推廣。

一個功能強(qiáng)大的通用串行解碼模塊,通過采用不同的解碼程序,能夠支持多種串行通信協(xié)議,包括全雙工和半雙工等模式。以BiSS為例,我們可以利用SPI的SCK來模擬MA信號,而MISO則可以用來模擬SL信號。然而,在使用這種方法時,我們需要注意以下三個關(guān)鍵問題:

首先,MCU硬件模塊的FIFO深度是一個需要仔細(xì)考慮的因素。有些MCU的SPI寄存器長度是固定的,這意味著在完成一幀BiSS通信時可能需要多次通信和中斷。這可能導(dǎo)致MA信號的波形不連續(xù),從而可能引發(fā)通信錯誤。

其次,我們需要關(guān)注MCU硬件模塊是否具備線延遲補(bǔ)償?shù)哪芰Α>哂芯€延遲補(bǔ)償能力的外設(shè)能夠更好地應(yīng)對實(shí)際應(yīng)用環(huán)境的變化,包括需求變化、環(huán)境變化以及線路老化等因素。這樣的系統(tǒng)具有更高的可靠性和適應(yīng)性,相較于沒有線延遲補(bǔ)償?shù)南到y(tǒng)更具優(yōu)勢。

最后,CRC解碼能力也是一個不可忽視的方面。CRC校驗(yàn)對MCU的處理能力提出了要求,因此選擇具備強(qiáng)大CRC解碼能力的MCU對于確保通信的準(zhǔn)確性和可靠性至關(guān)重要。

在使用MCU進(jìn)行解碼時,我們需要充分考察不同MCU外設(shè)的特點(diǎn)和處理能力,同時關(guān)注芯片廠家提供的技術(shù)支持力度以及是否有成熟的設(shè)計案例可供參考。這些因素將直接影響解碼的效率和穩(wěn)定性,因此需要我們進(jìn)行認(rèn)真評估和選擇。

三、混合解碼策略

對于那些既希望利用硬件解碼的優(yōu)勢,又想控制成本的用戶,混合解碼策略是一個值得考慮的方案。具體來說,我們可以利用FPGA或CPLD的部分資源來完成數(shù)據(jù)通信的任務(wù),而將關(guān)鍵的CDM和CDS信號的處理工作交給MCU進(jìn)行。這種策略雖然在某種程度上屬于過渡性質(zhì)的,但在實(shí)際應(yīng)用中卻展現(xiàn)出了極高的實(shí)用性。

值得注意的是,在使用這種混合解碼策略時,必須確保CDM信號在通信發(fā)起前已經(jīng)準(zhǔn)備好,以確保通信的順利進(jìn)行。然而,隨著MCU和FPGA技術(shù)的不斷進(jìn)步,這種混合解碼方案可能會逐漸被更為集成化的解決方案所替代,從而進(jìn)一步降低系統(tǒng)之間的耦合性,提高整體性能。

四、BiSS通信幀實(shí)例展示

為了更直觀地展示BiSS通信的過程,圖8給出了一個BiSS通信幀的實(shí)例。通過這個實(shí)例,讀者可以清晰地看到BiSS通信幀的結(jié)構(gòu)和各個組成部分,從而更好地理解和應(yīng)用BiSS通信協(xié)議。

圖8:BiSS通信幀實(shí)例

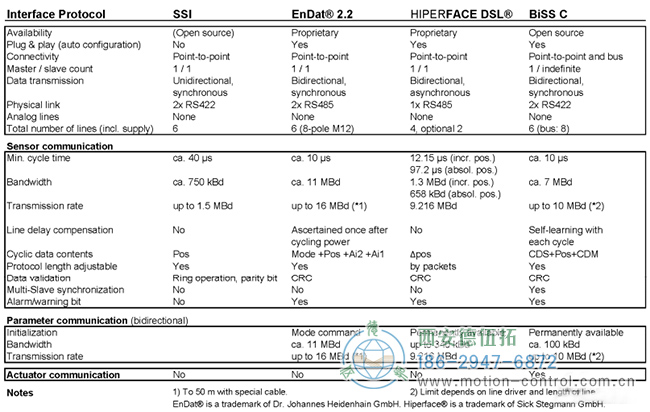

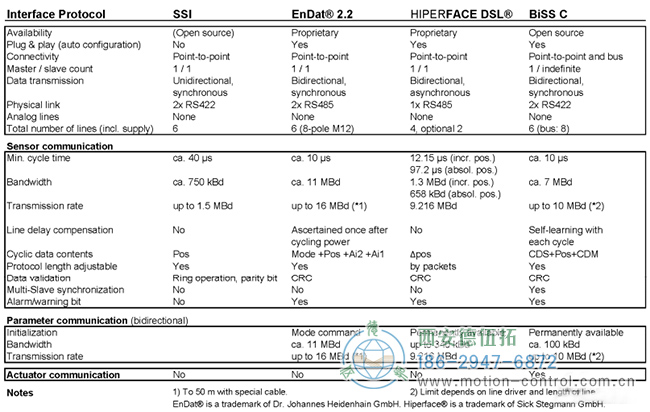

BiSS通信協(xié)議與其他通信協(xié)議的對比

BiSS通信協(xié)議相較于其他通信協(xié)議展現(xiàn)出了顯著的優(yōu)勢。根據(jù)下表1的對比數(shù)據(jù),我們可以清晰地看到,在協(xié)議開放性、網(wǎng)絡(luò)結(jié)構(gòu)以及線延遲補(bǔ)償?shù)确矫妫珺iSS通信協(xié)議均表現(xiàn)出領(lǐng)先的地位。尤其是在協(xié)議開放性(Availability)和網(wǎng)絡(luò)結(jié)構(gòu)(包括Connectivity、Master/Slave數(shù)量以及多從機(jī)同步Multi-Slave Synchronization)方面,BiSS協(xié)議展現(xiàn)出了明顯的優(yōu)勢。而在高速性(Transmission Rate)和時延(Min Cycle Time)方面,BiSS協(xié)議則與Endat2.2相當(dāng),表現(xiàn)出同樣出色的性能。

值得一提的是,BiSS通信協(xié)議的數(shù)據(jù)通信和寄存器通信占用的是不同的通信信道,這意味著兩者在通信過程中互不干擾,從而確保了通信的穩(wěn)定性和效率。這一特點(diǎn)使得BiSS通信協(xié)議在復(fù)雜的工業(yè)控制環(huán)境中更具優(yōu)勢。

表1:不同編碼器協(xié)議的參數(shù)對比

綜上所述,BiSS通信協(xié)議在多個方面均表現(xiàn)出明顯的優(yōu)勢,特別是在協(xié)議開放性、網(wǎng)絡(luò)結(jié)構(gòu)和線延遲補(bǔ)償?shù)确矫妗_@使得BiSS協(xié)議在工業(yè)自動化和編碼器通信領(lǐng)域具有廣泛的應(yīng)用前景。

BiSS通信協(xié)議的發(fā)展歷程與現(xiàn)狀

BiSS通信協(xié)議經(jīng)過十余載的深耕與積累,已經(jīng)在歐洲得到了廣泛的應(yīng)用。同時,在中國,這一協(xié)議也受到了主要驅(qū)動器及編碼器廠商的大力支持與認(rèn)可。回溯歷史,2002年BiSS協(xié)議首次在歐洲亮相,而在短短一年之后的2003年,BiSS解碼芯片IC-MB3便成功問世,這無疑為BiSS協(xié)議的普及與應(yīng)用奠定了堅實(shí)的基礎(chǔ)。隨后,在2009年,BiSS更是推出了單向通信版本,進(jìn)一步豐富了其應(yīng)用場景。

值得一提的是,BiSS總線幀格式始終保持穩(wěn)定,這使得眾多編碼器廠商能夠放心地推出基于BiSS的編碼器產(chǎn)品,進(jìn)一步推動了BiSS協(xié)議在市場上的普及。目前,全球已有超過278家廠商加入BiSS協(xié)議會員大家庭,共同推動這一協(xié)議的發(fā)展與進(jìn)步。

歐洲在工業(yè)控制領(lǐng)域一直處于領(lǐng)先地位,從CiA402、IEC61131-3等協(xié)議的發(fā)展歷程中,我們不難看出協(xié)議開放已經(jīng)成為行業(yè)發(fā)展的主流趨勢。BiSS協(xié)議在這方面已經(jīng)走在了前列,它為用戶帶來了兼容性、低成本和穩(wěn)定性等諸多優(yōu)勢。隨著工業(yè)自動化的不斷發(fā)展,相信在未來,BiSS協(xié)議在中國也將取得更加輝煌的成就。

了解更多

BiSS編碼器相關(guān)知識,敬請關(guān)注西安德伍拓自動化傳動系統(tǒng)有限公司網(wǎng)站。公司技術(shù)團(tuán)隊為您免費(fèi)提供編碼器的選型、安裝、調(diào)試、保養(yǎng)等技術(shù)指導(dǎo)服務(wù),盡量避免企業(yè)因?yàn)榫幋a器技術(shù)人員的短缺帶來的損失,采取拉線上+拉線下服務(wù)的服務(wù)形式,幫助企業(yè)解決技術(shù)難題。

在線QQ

在線QQ 186-2947-6872

186-2947-6872 在線咨詢

在線咨詢

info@motion-control.com.cn

info@motion-control.com.cn